Hot on the heels of the DE0-Nano and FMC interface board comes Zipper, a new interface board from Azio for the Myriad-RF 1 module, that enables it to be used with FPGA development boards that have either an FMC or HSMC connector.

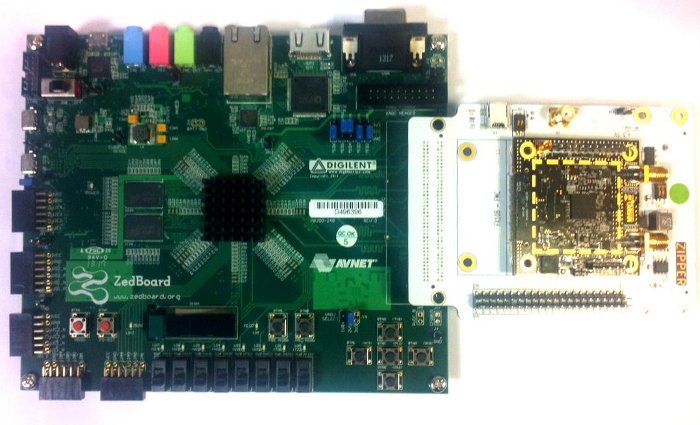

The board can be seen above being used together with a Xilinx ZedBoard, but the inclusion of both HSMC and FMC connectors means that it could equally be used with an Altera development board. In addition to which a 0.1” pitch header provides prototyping-friendly breakout of RF module I/O.

The Zipper board includes an Si5351C clock generator IC, along with a PLL that enables it to be used with an external clock source. SPI, GPIO and MIPI RF can be accessed via a USB interface, or alternatively the board can be configured for communication via FMC, HSMC or 0.1” header.

As with the RF module and the original DE0-Nano interface, KiCAD design files, PDF exports and Gerbers are available under the CC BY 3.0 licence and can be found on GitHub.

Control utility with Windows and Linux support

A new version of the control utility is being provided for use with the Zipper board and this is supported on both Windows and Linux. The utility allows for calibration of the LMS6002D transceiver, along with configuration of it and the clock generator and PLL.

Source code and binary builds have been published to GitHub. However, please note that we are still working on the build documentation and at present this only covers Windows.

Availability

Zipper isn’t available for purchase just yet and as soon as it is details will be posted here and to Twitter and Google Plus.

Andrew