Has the time for open source processors and SoCs finally arrived?

Open source designs for logic synthesis targeting FPGAs and ASICs are by no means new, with numerous industry and community initiatives that stretch back as far as the late 1990s. However, in recent years — and in particular over the last year or so — efforts appear to have redoubled, with developments that suggest that more widespread industry adoption may be on the horizon.

Before considering more recent developments, let’s first take a look at some earlier efforts.

A tale of two SPARCs

LEON2 architecture diagram. Source: esa.int.

LEON is a family of 32-bit processors based on the SPARC-V8 architecture, that was originally developed by the European Space Agency (ESA), before going on to be developed by Gaisler Research (subsequently becoming Aeroflex Gaisler and then more recently, Cobham). Described in VHDL, LEON can be implemented in programmable logic or manufactured into an ASIC.

Given its origins it shouldn’t be surprising to learn that LEON is designed for operation in the harsh space environment, with radiation hardened fault-tolerant versions of the processors.

LEON is dual-licensed; available under GPL/LGPL and also a proprietary license. Meaning that companies can buy out of any obligation to publish their modifications to a processor core.

The project was started by ESA back in late 1997. LEON 2 has been used in the Atmel AT697 and various SoCs. The latest generation of the processor core, LEON 4, was released in January 2010.

T2 processor floorplan. Source: wikipedia.org, CC BY-SA 3.0.

The OpenSPARC project was started by Sun Microsystems in 2005 and in 2006 they open sourced the complete design for their UltraSPARC T1 processor. This was followed in 2007 by the open sourcing of the T2 processor, which featured no less than 8 cores, 16 pipelines and 64 threads!

This was a bold move by Sun, who provided not only the Verilog RTL, but also a verification environment and diagnostic tests, along with tools for synthesis and simulation. In addition to which they supplied development kits to universities and even published a book on internals.

Open to the (IP) core

STREAM OpenRISC SoC block diagram

OpenCores is an open source hardware community developing IP cores such as processors and USB, Ethernet and other interface controllers, with many components supporting a non-proprietary system bus called Wishbone. Its roots can be traced back to around 1999 and by 2010, OpenCores boasted some 800 projects and 95,000 users, hitting the 150,000 user mark in 2012.

The flagship project is OpenRISC, which along with having created an open source RISC ISA with DSP features, has developed tools, libraries, operating system support and applications. Not to mention also system-on-chips and system simulators, with one that even runs in a web browser.

OpenRISC has been used in numerous ASICs, including Samsung digital television SoCs. A fault tolerant version of OpenRISC also flew in TechEdSat, the NASA CubeSat technology demonstrator. And of course there is an OpenRISC SoC for the Myriad-RF STREAM board.

RISC-V and lowRISC

lowRISC system diagram.

RISC-V originated in 2010 at UC Berkeley and was originally designed to support computer architecture research and education. However, it is now hoped that it will go on to become a standard open architecture for industry implementations. ISA specs are provided along with toolchains, a simulator and verification suite. Rocket, a 64-bit processor, is also available for high-speed simulation and full synthesis, with support for affordable FPGA development systems.

The lowRISC project builds on RISC-V and aims to provide fully open hardware systems, from the processor core to development board. The lowRISC SoC will benefit from novel features such as tagged memory for enhanced security, plus programmable I/O courtesy of “minion cores”.

Established as a non-profit in 2014, by the end of 2015 lowRISC plan to fabricate a dual-core test chip with memory PHY and minion cores in either 28nm or 40nm.

Collaboration and commercialisation

In addition to following in that great open source tradition of standing on the shoulders of giants and building on the work of others, technical advisers to lowRISC include Julius Baxter from the OpenRISC project and veteran hardware hacker, Bunnie Huang. Furthermore, there will be a European lowRISC and RISC-V workshop running as part of ORCONF this year, which has grown from purely an OpenRISC focus to covering wider open source digital design topics.

Collaborations such as these are key and central to the development of open source ecosystems. In this respect and others, great advances are now being made on earlier efforts. Which is not to downplay the significant IP contributions made by Sun or the effectiveness of the LEON project in meeting its objectives, but it does feel as though we have begun a new chapter in open source digital design, together with a palpable growth in interest, activity and commercial viability.

If all goes according to plan we should see the first lowRISC volume run some time within the next two years, with development boards following shortly after. There has also been the emergence of start-ups such as Nerabus that plan to build their own lowRISC-based silicon products.

Given the obvious differences, challenges and associated costs, it is hardly surprising that open source digital design has not progressed anywhere near as fast as the development of open source software. However, it does look as though exciting times are ahead and we look forward to further collaborating with the community!

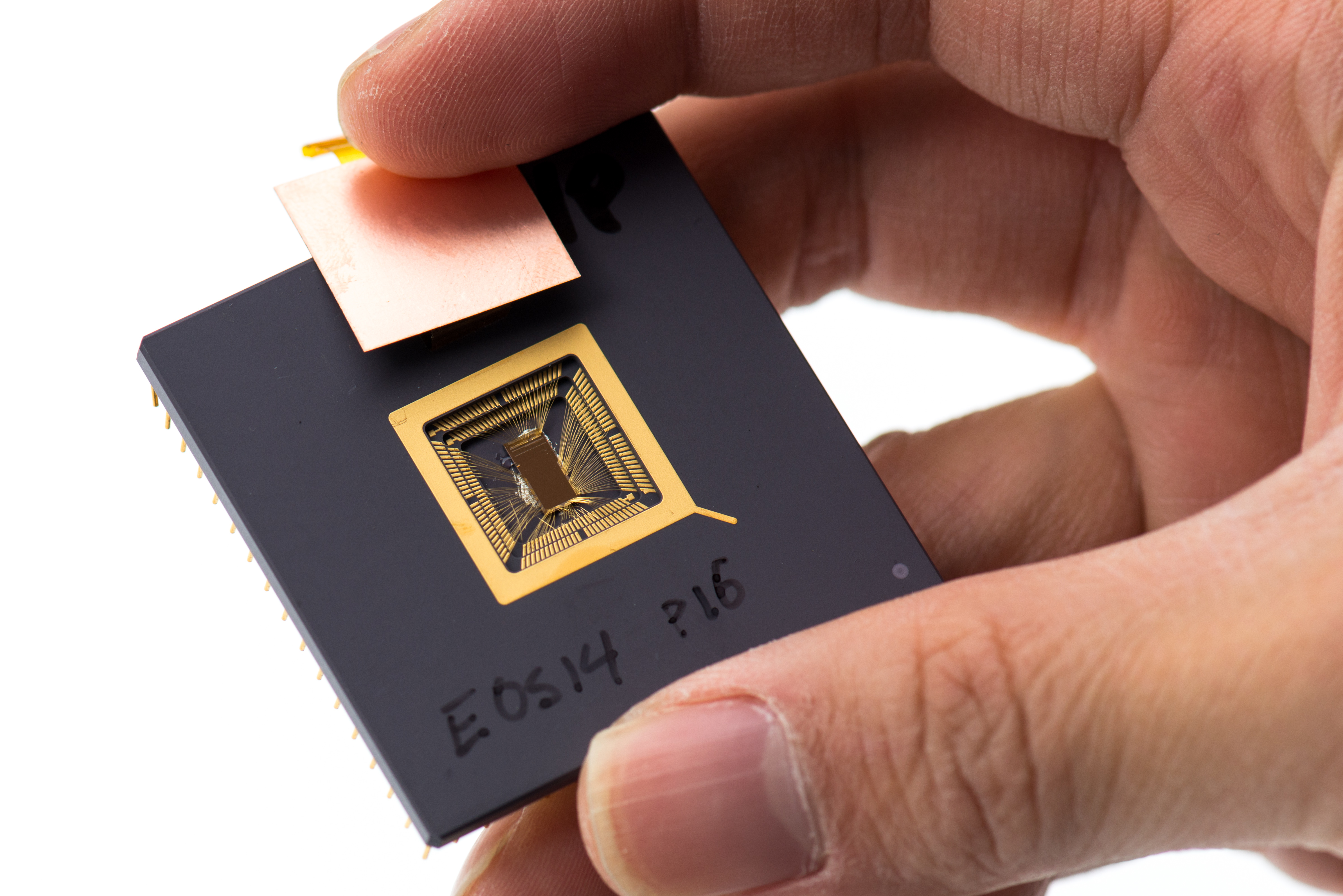

Top image: RISC V prototype chip at UC Berkeley Par Lab Winter Retreat, January 2013. CC0.