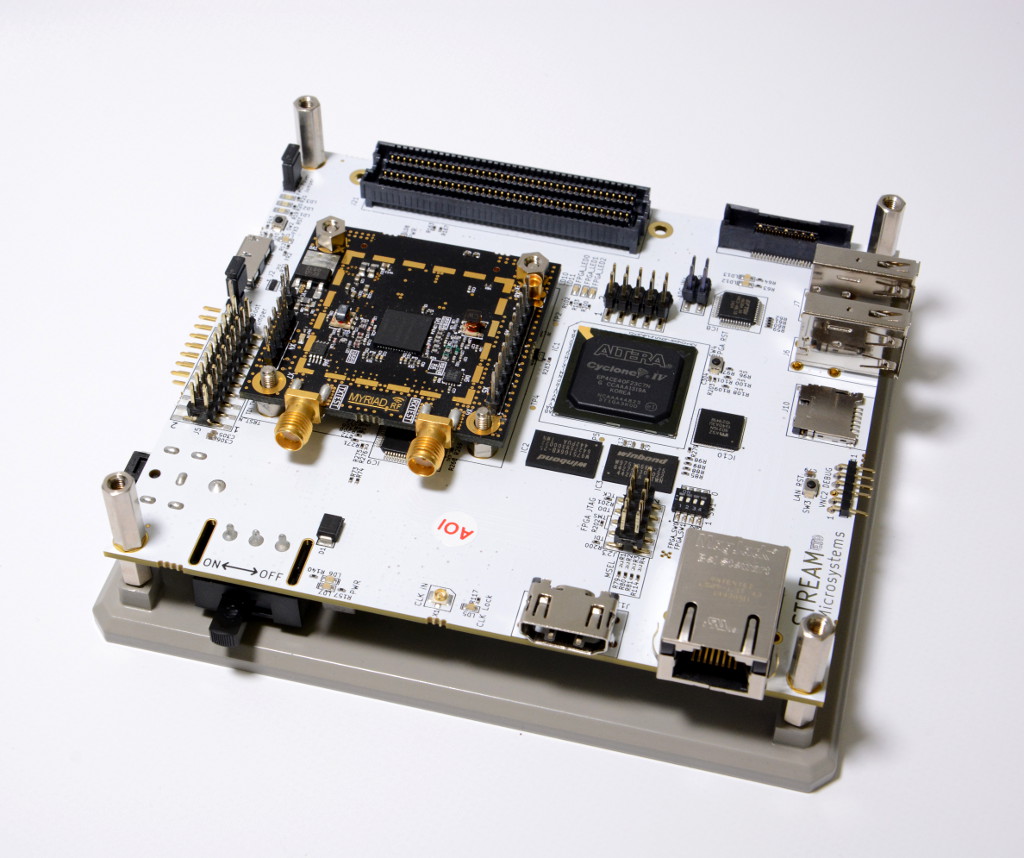

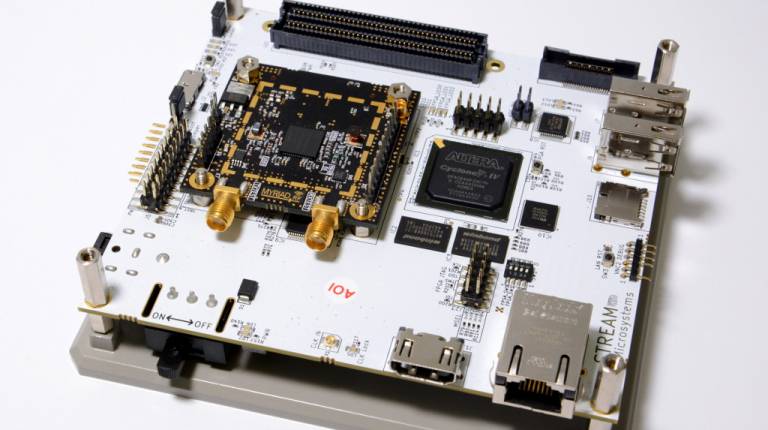

STREAM is a flexible platform for developing high-performance digital and RF designs using an Altera Cyclone IV FPGA and Lime Microsystems FPRF transceiver. It is available in its original form factor and a much more compact, lower cost micro variant.

STREAM

The original STREAM board incorporates SDRAM, Micro SD storage and a selection of other useful peripherals, with expansion via RFDIO and FMC mezzanine cards enabling use with both Myriad-RF 1 and LMS7002M EVB RF modules.

Software is provided for use with the LMS7002M EVB that allows control of the transceiver, ADC spectrum to be analysed via an FFT viewer, and example waveforms to be loaded into the FPGA.

An OpenRISC SoC is available that is capable of running Linux and bare metal applications, complete with a peripheral controller for interfacing RFDIO cards such as Myriad-RF 1. This allows for a mixed development model whereby programming and control is done via a flexible RISC processor, with baseband processing taking place directly in the FPGA fabric.

FPGA

- Cyclone IV EP4CE40F23C7N device in 484-pin FBGA

- 39’600 LEs

- 1134 Kbits embedded memory

- 116 embedded 18×18 multipliers

- 4 PLLs

- JTAG mode configuration

- Serial mode configuration via Cypress FX3

RAM and storage

- 2x64MB (16bit) SDRAM

- Micro SD with access via USB Host controller

Interfaces

- Micrel KSZ9021GN GbE controller

- Dual USB 2.0 host (VNC2-48L1B)

- Cypress FX3 USB 3.0 (CYUSB3013)

- DVI transmitter (TFP410)

Expansion

- FPGA Mezzanine Card (FMC) LPC connector

- RFDIO (FX80P) high-speed connector

- GPIO header

Programming and debug

- FPGA JTAG header (Altera USB-Blaster)

- Cypress FX3 JTAG header

- Mictor E5346A Agilent test equipment connector

Clock system

- 30.72MHz oscillator

- Programmable clock generator (SI5351C) for the FPGA reference clock input and RF mezzanine boards

- Locking to external clock circuit (ADF4002)

uSTREAM

At only 31mm x 108mm the uSTREAM is an incredibly compact solution that is able to accommodate both LMS6002D and LMS7002M variants of the uMyriadRF transceiver module. The digital signals are driven from the PC via a USB3.0 controller, or alternatively via a Raspberry Pi connector.

FPGA

- Cyclone IV EP4CE10F17C8N device in 256-pin FBGA

- 10’320 LEs

- 414 Kbits embedded memory

- 23 embedded 18×18 multipliers

- 4 PLLs

RAM

- 512M (32M x 16) bit DDR2 SDRAM

Interfaces

- Cypress FX3 Super Speed USB 3rdgeneration controller (CYUSB3013)

- 40-pin Raspberry Pi socket

Programming and debug

- JTAG mode configuration

- Serial mode configuration via Cypress FX3

Clock

- 30.72MHz on board TCXO

- 8-bit DAC (TCXO frequency adjustment)